# LABORATORY MANUAL

For

# **E-CAD LAB**

(III B. Tech ECE- II Semester- R18 .AY:2021 - 22)

**Prepared by**

1. Mr. M. RANJITH REDDY, Asst. Professor

2. Mr. K. RAJESH, Asst. Professor

**Department of**

Electronics & Communication Engineering 2022

www.siddhartha.co.in

# **CONTENTS**

| S. No | Description                                        | Page No. |

|-------|----------------------------------------------------|----------|

| 1     | Vision & Mission of the Institute                  | i        |

| 2     | Vision & Mission of the Department                 | ii       |

| 3     | Program Outcomes                                   | iii      |

| 4     | Rules and Regulations of Lab                       | iv       |

| 5     | Introduction to Xilinix                            | 1-11     |

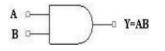

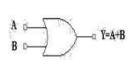

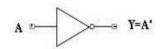

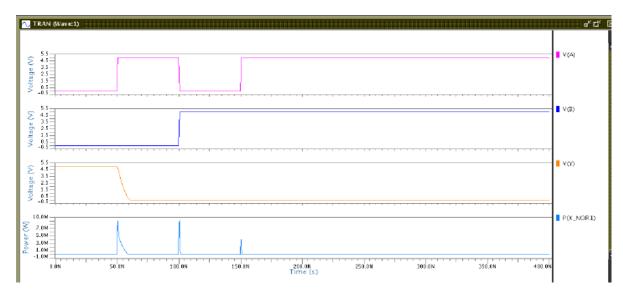

| 6     | HDL code to realize all logic gates                | 12-13    |

| 7     | Design of 2-to-4 encoder                           | 15-16    |

| 8     | Design of 8-to-3 encoder                           | 17-19    |

| 9     | Design of 8-to-1 multiplexer and 1x8 demultiplexer | 20-21    |

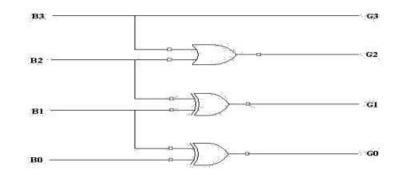

| 10    | Design of 4 bit binary to gray code converter      | 22-23    |

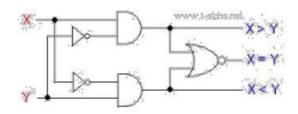

| 11    | Design of 4-bit comparator                         | 24-26    |

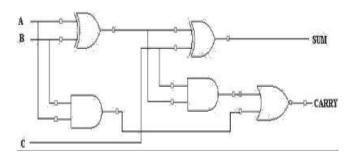

| 12    | Design of full adder using three modelling styles  | 27-32    |

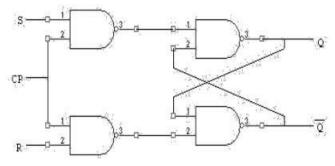

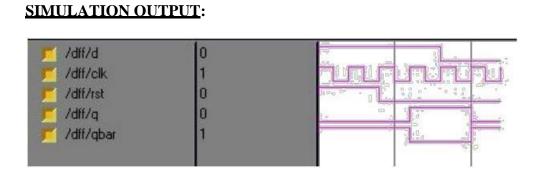

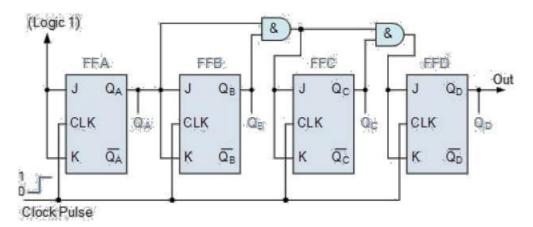

| 13    | Design of flip flops (SR,JK,D,T)                   | 33-35    |

| 14    | Finite state machine design                        | 36-37    |

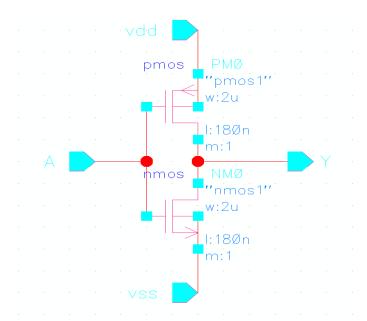

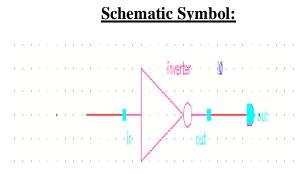

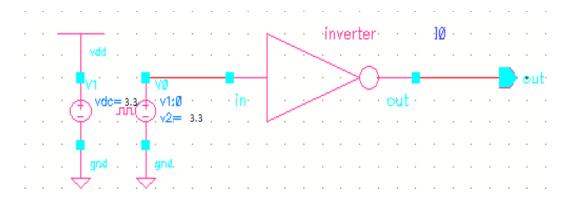

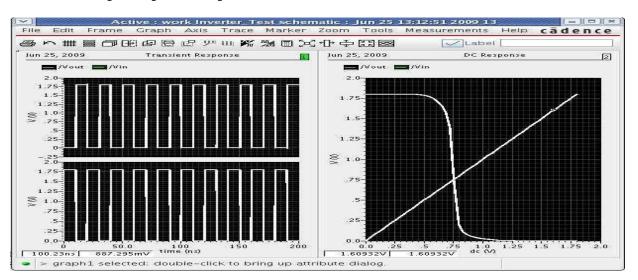

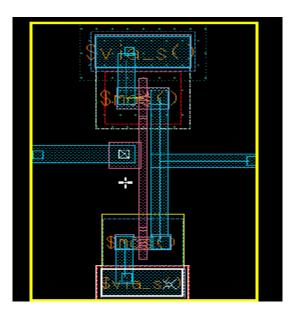

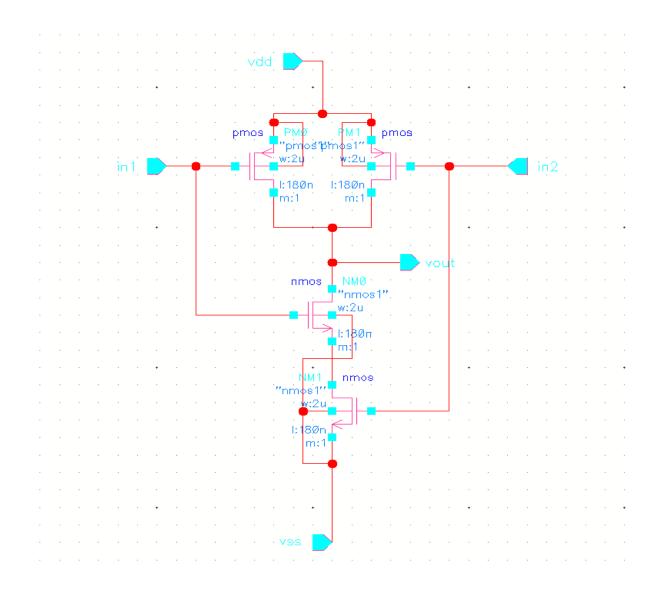

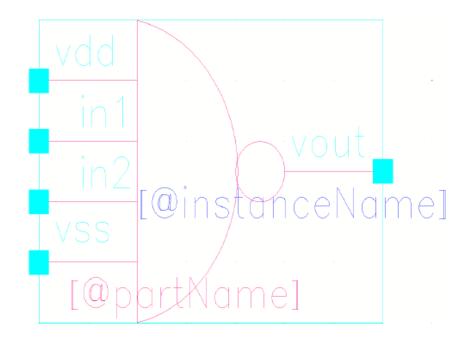

| 15    | Design & Implementation of an Inverter             | 38-40    |

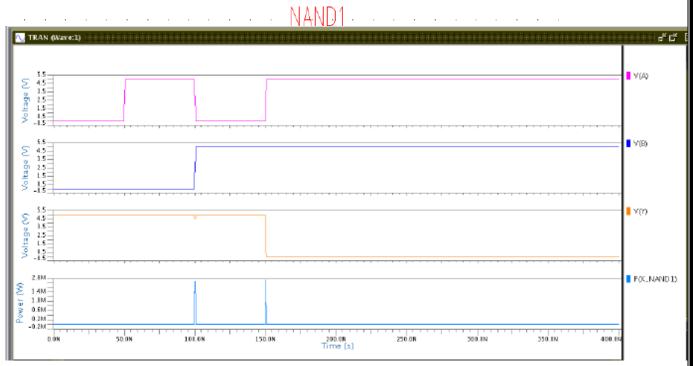

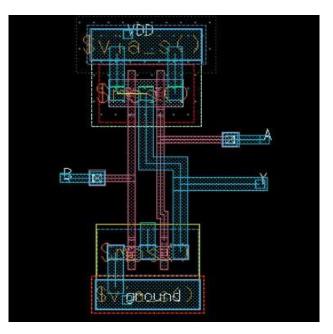

| 16    | NAND Gate                                          | 41-44    |

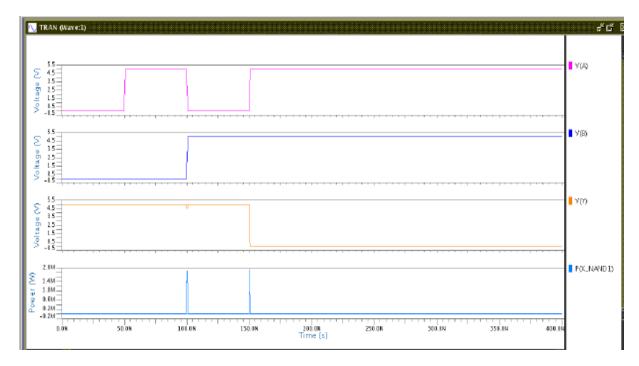

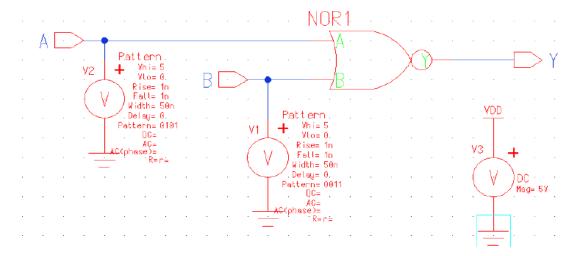

| 17    | NOR Gate                                           | 45-47    |

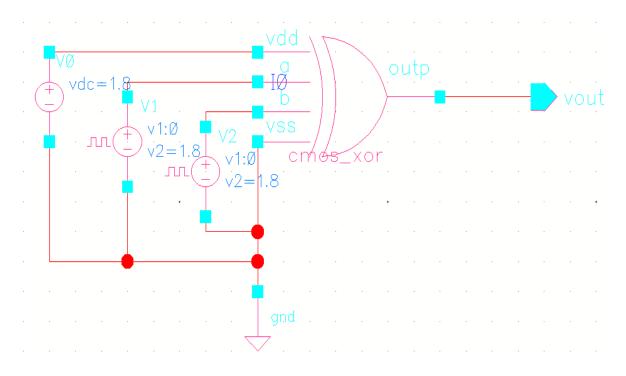

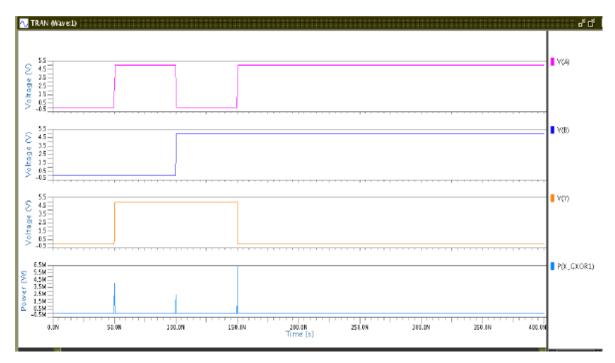

| 18    | X-OR Gate                                          | 48-52    |

| ADDITIONAL<br>EXPERIMENTS |  |  |  |  |  |  |  |

|---------------------------|--|--|--|--|--|--|--|

|                           |  |  |  |  |  |  |  |

|                           |  |  |  |  |  |  |  |

# **VISION & MISSION OF THE INSTITUTE**

# VISION:

To be a Centre of Excellence in Technical Education and to become an epic center of Research for creative solutions.

# **MISSION:**

To address the Emerging Needs through Quality Technical Education with an emphasis on practical skills and Advanced Research with social relevance.

# **OBJECTIVES:**

- To translate our vision into action and accomplish our mission, we strive to provide state-of-art infrastructure.

- Recruit, Motivate and develop faculty of high caliber and with multiple specialization.

- Continuously review, innovate and experiment teaching methodologies and learning processes.

- Focus on research, training and consultancy through an Integrated Institute-Industry symbiosis.

# **VISION & MISSION OF THE DEPARTMENT**

# **VISION:**

To provide innovative teaching and learning methodologies for excelling in a high-value career, higher education and research to the students in the field of Electronics and Communication Engineering to meet the needs of the industry and to be a part of the advancing technological revolution.

# **MISSION:**

- To create engineers of high quality on par with international standards by providing excellent infrastructure and well qualified faculty.

- To establish centers of excellence to enhance collaborative and multidisciplinary activities to develop human and intellectual qualities.

- To provide technical expertise to carry out research and development.

# PROGRAM EDUCATIONAL OBJECTIVES (PEOS) :

Graduates shall apply the fundamental, advanced and contemporary knowledge of

- 1. Electronics, Communication and allied Engineering, to develop efficient solutions and systems, to meet the needs of the industries and society.

- 2. Graduates will get employed or pursue higher studies or research.

- 3. Graduates will have team spirit, good communication skills and ethics with lifelong learning attitude.

#### **PROGRAM OUTCOMES:**

#### Engineering Graduates will be able to:

- 1. **Engineering Knowledge:** Apply the knowledge of mathematics, science, engineering fundamentals, and an engineering specialization to the solution of complex engineering problems.

- 2. **Problem analysis:** Identify, formulate, review research literature, and analyze complex engineering problems reaching substantiated conclusions using first principles of mathematics, natural sciences, and engineering sciences.

- 3. **Design/development of solutions:** Design solutions for complex engineering problems and design system components or processes that meet the specified needs with appropriate consideration for the public health and safety, and the cultural, societal, and environmental considerations.

- 4. **Conduct investigations of complex problems:** Use research-based knowledge and research methods including design of experiments, analysis and interpretation of data, and synthesis of the information to provide valid conclusions.

- 5. **Modern tool usage:** Create, select, and apply appropriate techniques, resources, and modern engineering and IT tools including prediction and modeling to complex engineering activities with an understanding of the limitations.

- 6. **The engineer and society:** Apply reasoning informed by the contextual knowledge to assess societal, health, safety, legal and cultural issues and the consequent responsibilities relevant to the professional engineering practice.

- 7. Environment and sustainability: Understand the impact of the professional engineering solutions in societal and environmental contexts, and demonstrate the knowledge of, and need for sustainable development.

- 8. **Ethics:** Apply ethical principles and commit to professional ethics and responsibilities and norms of the engineering practice.

- 9. **Individual and team work:** Function effectively as an individual, and as a member or leader in diverse teams, and in multidisciplinary settings.

- 10. **Communication:** Communicate effectively on complex engineering activities with the engineering community and with society at large, such as, being able to comprehend and write effective reports and design documentation, make effective presentations, and give and receive clear instructions.

- 11. **Project management and finance:** Demonstrate knowledge and understanding of the engineering and management principles and apply these to one's own work, as a member and leader in a team, to manage projects and in multidisciplinary environments.

- 12. Life-long learning: Recognize the need for, and have the preparation and ability to engage in independent and life-long learning in the broadest context of technological change.

# **INTRODUCTION - XILINX**

**Xilinx ISE** is a software tool produced by Xilinx for synthesis and analysis of HDL designs, which enables the developer to synthesize ("compile") their designs, perform timing analysis, examine RTL diagrams, simulate a design's reaction to different stimuli, and configure the target device with the programmer.

In our Lab, the scope is limited to design and analyze the design using test benches & simulation.

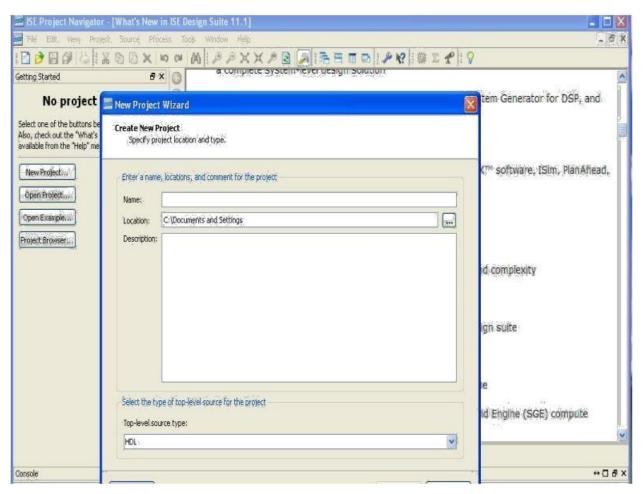

The following is the step by step procedure to design in the Xilinx ISE:

1. New Project Creation

Once the Xilinx ISE Design suite is started, open a new project & enter your design name and the location path. By default 'HDL' is selected as the top-level source type. (If not, please select Top-level source type as 'HDL')

2. Continue to the next window and check if the Preferred Language is selected as 'Verilog'

| No project                                                                  | 🖾 New Project Wizard                                   |                         | tem Generator for DSP, and               |

|-----------------------------------------------------------------------------|--------------------------------------------------------|-------------------------|------------------------------------------|

| t one of the buttons be<br>check out the "What's<br>able from the "Help" me | Device Properties<br>Specify device and project proper | ies.,                   |                                          |

| wProjection                                                                 | Select the device and design flow for t                | se project              | K <sup>m</sup> software, ISim, PlanAhead |

| en Project                                                                  | Property Name                                          | ) Value                 |                                          |

|                                                                             | Product Category                                       | General Purpose         |                                          |

| en Examples a                                                               | Family                                                 | CoolRunner XPLA3 CPLDs. | ~                                        |

| ect Browser                                                                 | Device                                                 | Automatic xcr3000xl     | ~                                        |

|                                                                             | Package                                                |                         | ~                                        |

|                                                                             | Speed                                                  |                         | id complexity                            |

|                                                                             | Top-Level Source Type                                  | HÖL                     | 82                                       |

|                                                                             | Synthesis Taol                                         | (XST (VHDE/Werllog)     |                                          |

|                                                                             | Simulator                                              | Modelsim-SE Mixed       | ign suite                                |

|                                                                             | Preferred Language                                     | Verilog                 |                                          |

|                                                                             | Manual Comple Order                                    |                         |                                          |

|                                                                             | Enable Enhanced Design Summary                         |                         | le                                       |

|                                                                             | Enable Message Filtering                               |                         | itica anna fhitea ainmeistea.            |

|                                                                             | Display Incremental Messages                           | 1                       | id Engine (SGE) compute                  |

3. Proceed by clicking 'Next' and create a 'New Source' using the 'Create New Source' Window

| check out the "What's<br>able from the "Help" me<br>w Project |           | one source at this time. You ca<br>e "Project->New Source" comm                                                   | in add existing sources on the ne<br>and. | xt págó, and later créate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | K <sup>**</sup> software, ISim, Pla | nAhead |

|---------------------------------------------------------------|-----------|-------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|--------|

| en Project.cov                                                | j Sou     | rcé File                                                                                                          | Туре                                      | New Source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                     |        |

| n Example                                                     | 8         | E                                                                                                                 |                                           | ( Retreas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                     |        |

| ct Browser                                                    |           | <u> </u>                                                                                                          | ň:                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                     |        |

|                                                               |           | Mew Source Wiz                                                                                                    | ard                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | X                                   |        |

|                                                               |           | Select Source Typ<br>Select source by                                                                             | e<br>pe, file name and its location.      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                     |        |

|                                                               |           | III a const                                                                                                       |                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                     |        |

|                                                               |           | Schemetic     Schemetic     User Document     Verlog Module     Verlog Test Pixtu     VHDL Module     MHDL Ubrary | rė                                        | File name:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                     |        |

|                                                               |           | VHDL Package                                                                                                      |                                           | logicgates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1                                   | 10     |

|                                                               |           | YHDL Test Bench                                                                                                   |                                           | Location:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                     | ite    |

|                                                               |           |                                                                                                                   |                                           | Cil/Documents and Settl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ngs\logicgates                      | -      |

|                                                               |           |                                                                                                                   |                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                     |        |

|                                                               | More Info |                                                                                                                   |                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                     | -      |

|                                                               |           |                                                                                                                   |                                           | and the second se |                                     |        |

**4.** Select the source type as 'Verilog Module' and input a filename and proceed to 'Next'. In the next window 'Define Module' enter the ports.

| A Project    | a á hewi spurcé           | K <sup>m</sup> software | , ISim, PlanAhe |     |     |

|--------------|---------------------------|-------------------------|-----------------|-----|-----|

| m Projection | Source File               | Туре                    | New Source      |     |     |

| n Examples.  |                           |                         | . Attinte       |     |     |

|              |                           |                         | - 329(1/2752    |     |     |

| ct Browser/d | 6                         |                         |                 |     | -   |

|              | New Source Wizard         | 111222-01               |                 |     |     |

|              | Thew source wizero        |                         |                 |     | 1.1 |

|              | Define Module             |                         |                 |     |     |

|              | Specify ports for module. |                         |                 |     |     |

|              |                           |                         |                 |     |     |

|              | Module name logicgates    |                         |                 |     |     |

|              | Port Name                 | Direction B             | us MSB          | 158 |     |

|              | A                         | iniput : 💌 🖂            |                 |     |     |

|              | В                         | input 🛛 💌 🖂             |                 |     |     |

|              | Aton                      | output 🔽 🖸              |                 | -   | ité |

|              | andAB                     | output 🛛 🖌              |                 |     |     |

|              | orAB                      | output 🛛 🔽              |                 |     |     |

|              | nandA8                    | output 🛛 👻 🖂            |                 |     |     |

|              | norAB                     | output 💌 🔄              |                 |     |     |

|              | xorA8                     | output 🛛 💙 🖸            |                 |     |     |

|              | Info -                    | output 💟 🔽              |                 | 5   |     |

|              | Info xnor48               |                         |                 |     |     |

|              | 1000                      | inpút. 🗸 🖸              |                 |     |     |

5. Finish with the New project setup with the 'Summary' window.

| Source Type<br>Source Name<br>Module name | tory: C:\Docume<br>: Verilog Module<br>e: logicgates.v<br>e: logicgates                   | ents and Settings logicg                             | ates:                                                                      |           |

|-------------------------------------------|-------------------------------------------------------------------------------------------|------------------------------------------------------|----------------------------------------------------------------------------|-----------|

| Port Definitio                            | A<br>B<br>notA<br>andA8<br>orA8<br>nandA8<br>nandA8<br>norA8<br>xorA8<br>xorA8<br>xnoirA8 | Pin<br>Pin<br>Pin<br>Pin<br>Pin<br>Pin<br>Pin<br>Pin | input<br>input<br>output<br>output<br>output<br>output<br>output<br>output |           |

| More Info                                 | xhorAB                                                                                    |                                                      |                                                                            | sh Cancel |

6. Once 'Finish' is selected a pop-up appears to create the directory. Select 'yes'

| Add to Project: Yes                                                                                                                                            | 🔤 Proje | ect Navigator 🛛 🔣                                                                                       |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------------------------------------------------------------------------------------------------------|--|

| Source Directory: C:(Docu<br>Source Type: Verilog Modu<br>Source Name: logicgates.)<br>Module name: logicgates<br>Port Definitions:<br>A<br>B<br>notA<br>andAB | ?       | The directory<br>'C:\Documents and Settings\logicgates'<br>does not exist. Would you like to create it? |  |

| orAB<br>nandAB                                                                                                                                                 | Pin     | output ;<br>output ;                                                                                    |  |

| norAB                                                                                                                                                          | Pin     | output                                                                                                  |  |

| ×orAB<br>×norAB                                                                                                                                                | Pin     | output:<br>.output:                                                                                     |  |

| Series con-                                                                                                                                                    |         |                                                                                                         |  |

7. Then proceed to 'Next' in the "New Project Wizard' to 'Add Existing Sources'. 'Add source' if an existing source is available, If not proceed to 'Next' and finish with the 'Project Summary' window

| No project                                                             |                                                                                                                                  | tem Generator for DSP, and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No project                                                             | New Project Wizard                                                                                                               | A notice interesting and the second s |

| one of the buttons be<br>heck out the "What's<br>le from the "Help" me | Project Summary<br>Project Navigator will create a new project with the following specifications:                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Project                                                                | Project Path: C:\Documents and Settings\logicgates<br>Working Directory:<br>Description:<br>Top Level Source Type: HDL           | K <sup>ee</sup> software, ISim, PlanAhead                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Examplean                                                              | Device:                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| t Browser                                                              | Device Family: CoolBunner XPLA3 CPLDs<br>Device: xcr3*x1<br>Package: *<br>Speed: -*                                              | ed complexity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                        | Synthesis Tool: XST (VHDL/Verilog)<br>Simulator: Modelsim-SE Mixed<br>Preferred Language: Verilog<br>Manual Compile Order: false | ight soite                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                        | Enhanced Design Summary: enabled<br>Message Filtering: disabled<br>Display Incremental Messages: disabled                        | ie<br>id Engine (SGE) compute                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                        | New Source:<br>Verilog Module logicgates.v                                                                                       | in cilline fage) comprée                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                        |                                                                                                                                  | ++                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                        | More Info                                                                                                                        | Cancel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

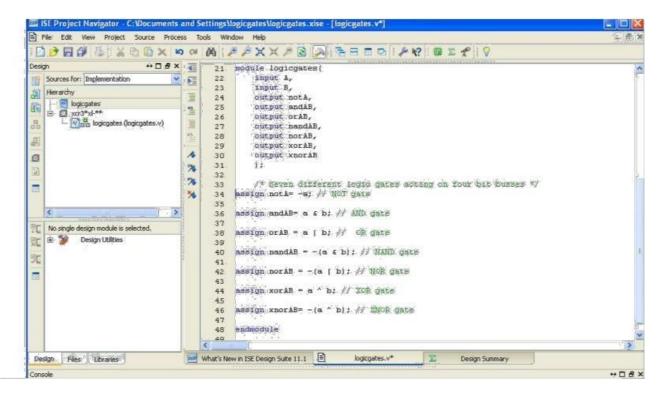

#### 8. Design Entry and Syntax Check

The ports defined during the 'Project Creation' are defined as a module in the 'filename.v' file

| a second second |  | A Concestor: Implementation     A Concestor: Implementatin     A Concestor: Implementatin     A Concestor: Implementatin | A PAXX P Page Page P | titt i |

|-----------------|--|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

|-----------------|--|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

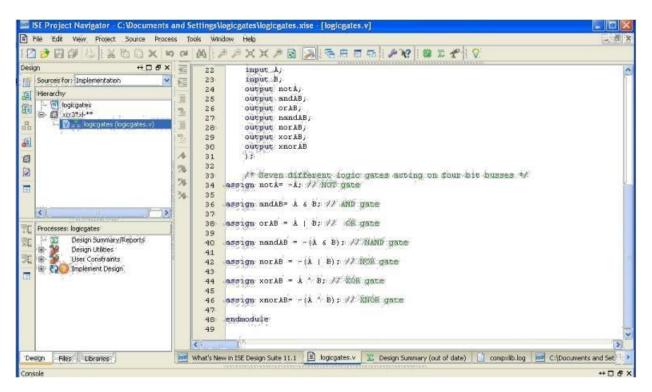

9. Input your design (verilog code) within the module definition

*10.* Select the design from the 'Hierarchy' window. In the below window of Processes 'Implement Design 'would be orange (in color) ready for implementation

11. Double click on implement design, it turns green (in color) once the design is implemented successfully and the Summary report is displayed.

| -5          | 0 × 0 0 × 0 0 × 0                                                                                                                                                                        | a A PPXX                                                                                                        |                             |               |                   |            | - No.                         |  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-----------------------------|---------------|-------------------|------------|-------------------------------|--|

| 目目          | Sources for: Implementation                                                                                                                                                              | E XILINX                                                                                                        | CPLD Rep                    | orts          |                   | C          | Runner                        |  |

| E           |                                                                                                                                                                                          | 13                                                                                                              | Fitter Report               | Timing Report |                   |            | 10.15m 11 152.52              |  |

|             | L Die logicgates (logicgates.v)                                                                                                                                                          | Fitter Report                                                                                                   |                             |               | Summary           |            |                               |  |

| a           |                                                                                                                                                                                          | A.777                                                                                                           | Design                      | Name          | logicigates       |            |                               |  |

| 2           | e i libri                                                                                                                                                                                | A CONTRACTOR AND A CONTRACTOR                                                                                   | Fitting                     | Status        | Successful        |            |                               |  |

|             | Contra Contra                                                                                                                                                                            | all for the second s | Softwar                     | e Version     | L.33              |            |                               |  |

|             | C                                                                                                                                                                                        | 1. 2. 2. 2.                                                                                                     | Device                      | Used          | XCR3032XL         | 5-PC44     |                               |  |

| e.          | Processes: logicgates                                                                                                                                                                    | Automotion Designed<br>There is a period                                                                        | Date                        |               | 6-26-2012, 1      | 0.51AM     |                               |  |

| ·<br>武<br>王 | Design Summary/Reports<br>Design Utilities<br>Liser Constraints                                                                                                                          |                                                                                                                 | RESOURCES SUMMARY           |               |                   |            |                               |  |

|             | Inclement Description     Inclement Description     Synthesize - XST     Sono - XST     Translate     Translate     Translate     Configure Target Device     Optional Implementation To | Equation                                                                                                        | Macrocells<br>Used          | Pterms Used   | Registers<br>Used | Pins Used  | Function Block<br>Inputs Used |  |

|             |                                                                                                                                                                                          | Display Style                                                                                                   | 7/32 (22%)                  | 7/96 (8%)     | 0/32 (0%)         | 9(32 (29%) | 2/80 (3%)                     |  |

|             |                                                                                                                                                                                          | VHDL 💌                                                                                                          | LOCAL CONTROL TERMRESOURCES |               |                   |            |                               |  |

|             |                                                                                                                                                                                          |                                                                                                                 | 1                           | LCT0 LCT1     | LCT2 LCT3         | LCT4 LCT5  | LCT6 LCT7                     |  |

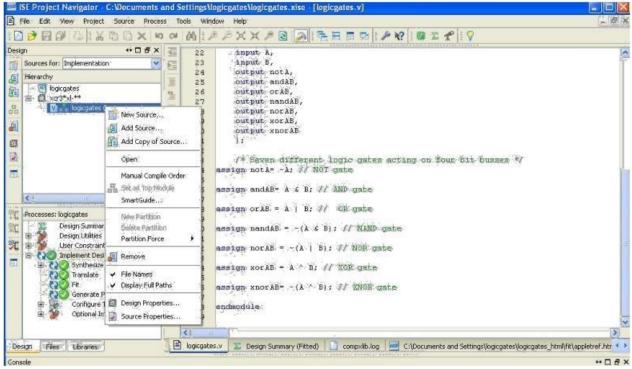

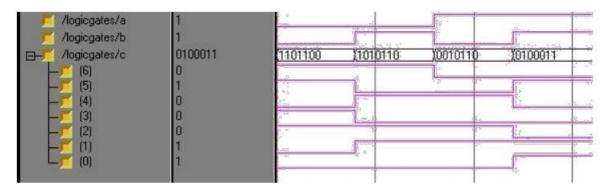

#### 12. Test-Bench creation, Simulation & Verification

To add a test-bench to the existing design, right click on the '.v' file from the Hierarchy window and select 'New Source'

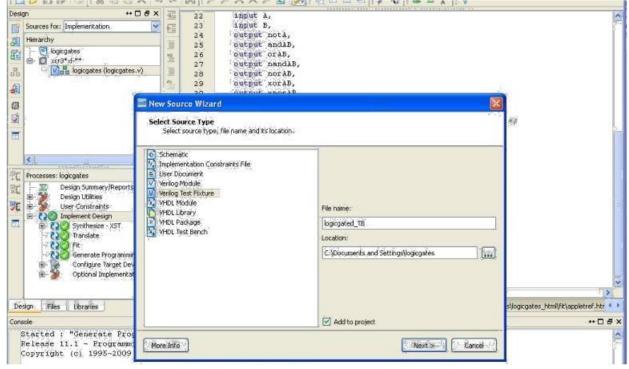

#### 13. Select 'Verilog Text Fixture' from the Select Source Type and name the Test-Bench

14. Continue to 'Finish' and a test bench is added in the project area

| BO AIXBOX .                                                                                                                      | ₩ ×××× × × × × × × × × × × × × × × × × | 1000       |

|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|------------|

| ign. ++ □ 6 ×<br>Sources for: Implementation<br>Herarchy<br>Ingrcgates<br>Ingrcgates (logicgates.v)<br>Ingrcgates (logicgates.v) |                                        | 292<br>292 |

|                                                                                                                                  | 27 // Inputs<br>28 reg A:<br>29 reg R: | 151        |

15. Edit the test bench as per your simulation requirements and select 'Behavioral Simulation' in the 'Design Window'. In the Processes window Isim Simulator would be displayed. First

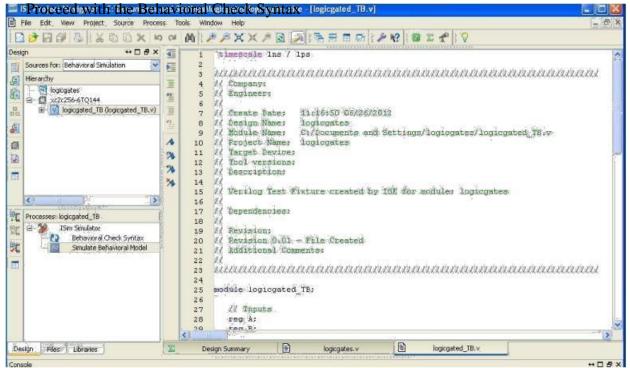

# 16. Double click on 'Behavioral Check Syntax' & check for no errors

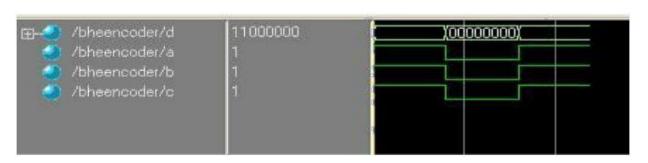

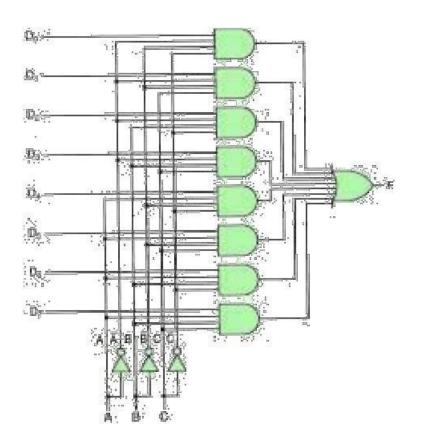

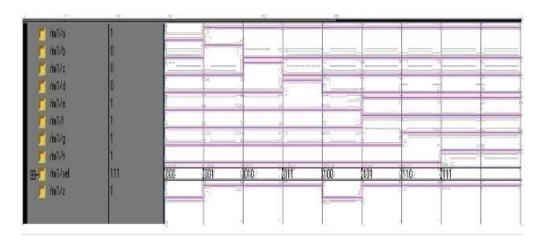

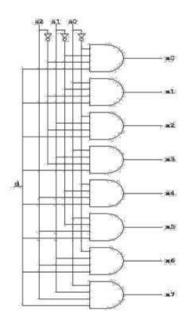

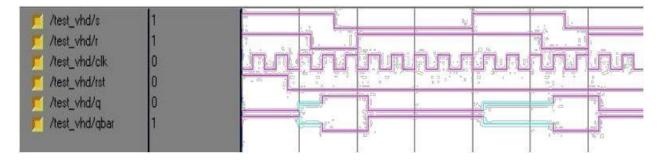

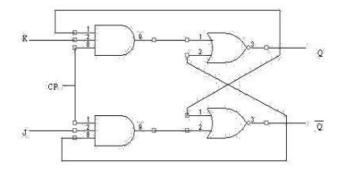

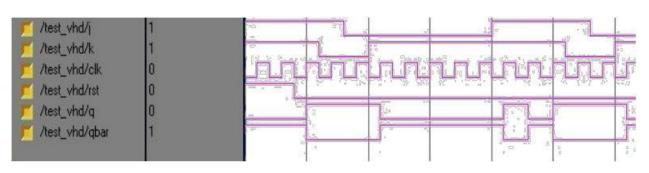

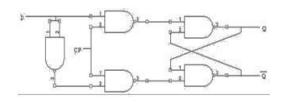

|     | Sources for: Behavioral Sinulation  Herarchy  Herarchy  Kocc256-61Q144  Brocesses: logicgated_TB (logicgated_TB.v)  Processes: logicgated_TB Behavioral Check Synkax Simulate Behavioral Model |                | 4 7/ Company<br>5 7/ Engine<br>6 7/<br>7 7/ Dubite<br>8 7/ Design<br>9 7/ Rodule<br>10 7/ Rodule<br>10 7/ Rodule<br>10 7/ Rodule<br>11 7/ Tagal v<br>13 7/ Depend<br>16 7/<br>19 7/ Depend<br>16 7/<br>19 7/ Reviss<br>20 7/ Reviss<br>20 7/ Reviss<br>20 7/ Reviss<br>21 7/ Additi<br>22 7/<br>23 7/7/7/7/<br>24<br>25 module 10<br>26 7/ Tup | Y:<br>Dhtes:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Name:<br>Na | 11136150 OGACGA<br>Dourogates<br>Dourogates<br>inglogates<br>Secore scented by<br>- File Dreated<br>methan<br>//////////////////////////////////// | lats<br>I Sefeknar<br>I 182 Eec | ************************************** |          |